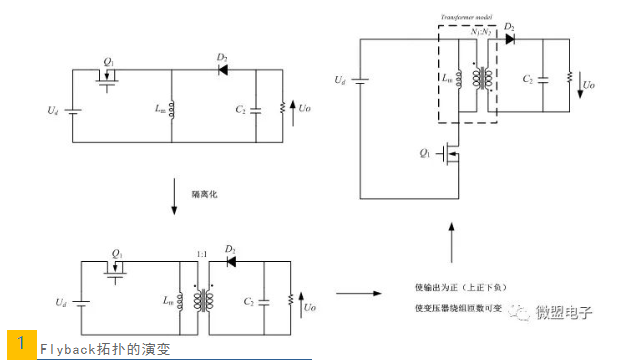

簡單(dān)回顧(gù)一下反(fǎn)激變換的基本原理,Flyback拓撲源於六種基本DC-DC電路之(zhī)一(yī)的(de)Buck-Boost,如下圖所示,Buck-boost電路在連續模式(CCM)下的直流增益是-D/(1-D),輸出電壓極性相反,如果對Buck-Boost進(jìn)行隔離化,同時使變壓器的線圈匝數可變並變(biàn)換輸出(chū)極性,就得到了一個Flyback電路(lù)。

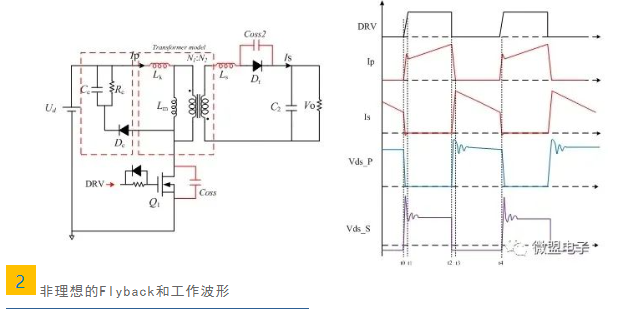

Flyback的(de)工作模式也和(hé)大多(duō)數開關電源一樣,可(kě)以工作在(zài)連續模式(CCM)、斷續模式(DCM)和(hé)臨界(jiè)導通模式(BCM)。如下圖所示,以工作在連續模式(CCM)的反(fǎn)激為例,可(kě)以看到理想(xiǎng)的(de)變壓器模型中還(hái)會存在漏感,實際等效電(diàn)路中還包括了RCD snubber吸(xī)收(增加阻(zǔ)尼,降低Q值),次邊的寄(jì)生電感Ls與續流二極管串聯(包含(hán)了雜散電感、副(fù)邊漏感),以及圖中未表示(shì)完全的各(gè)種寄生的感抗與容抗分布參數。下圖(tú)給出了驅動信號DRV、原邊電流Ip、次邊電流Is、原邊功率極的漏端(duān)電壓Vds_P和次邊同步(bù)整流管的Vds_S(或續(xù)流二極管的(de)反(fǎn)向壓差)。簡單來說,從t0~t2階(jiē)段,勵(lì)磁電感(gǎn)Lm儲能;t2~t4階段,勵磁電(diàn)感(gǎn)儲存(cún)的能量通過變壓器(qì)傳遞到副邊給輸出電容充電。圖中的t2~t3示意性給出了實際工作中存在的換流過(guò)程。

為什麽要加柵極的驅動緩衝(chōng)

01

優化EMI性能

EMI包(bāo)括傳導和輻(fú)射,前者通過寄(jì)生阻抗和其他連接以傳導方式耦合到原件,後者通過磁(cí)場能量以無線(xiàn)方(fāng)式傳輸到(dào)待測器件。

回顧下麥克斯韋方程組中的法拉第電磁感應定律:穿過一個曲麵的磁(cí)通的(de)變化會在此曲麵的(de)任意邊界路徑(jìng)上產生感應電動(dòng)勢,變化的(de)磁場產生環繞的電場。對於輻射而(ér)言,每個環路(lù)都是一個小的天線(xiàn),環路麵積的(de)大小(xiǎo)、負載電流的大小、測試距離的遠近、工作頻率(lǜ)的高低、測試方向夾角的差異,都會(huì)對輻射產(chǎn)生影(yǐng)響。通過布局的優化、降低di/dt和dv/dt噪聲(shēng)、增加EMI濾(lǜ)波等都可以優化EMI。

02

降低次邊續流功率二極管的電壓應力

03

從電路設計的角度出發(fā)可做哪些優化?

實現這種驅動速度調整的方法有很多(duō),比如可以集成(chéng)一個簡單的逐次逼近的SAR ADC,通(tōng)過一個時鍾沿觸發異步時鍾,通(tōng)過SAR邏輯的控製,對驅動(dòng)MOS的柵極信號從0到Miller平台到來(lái)之間(jiān)的時間差進行量化(huà),通過閉環(huán)與目標值進行比較進行調整,直到驅動速度穩定;也可以直接對表征上升沿速度的脈衝信號進行低通濾波獲得表(biǎo)征(zhēng)占空比信(xìn)息(xī)的電壓信號,對此(cǐ)電壓信號進行(háng)誤差調整。